Intel представила второе поколение нейроморфных чипов: Loihi II. Идейно и архитектурно новый чип, в целом, повторяет первое поколение, анонсированное четыре года назад, однако имеет целый ряд улучшений технического и программного характера. Но что более интересно, с выходом Loihi II, который всё ещё считается исследовательской разработкой, компания готова сделать первые шаги по ограниченной коммерциализации данного решения.

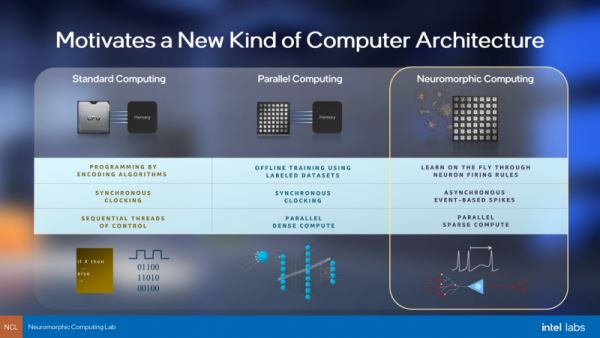

В рамках нейромофорного подхода исследователи пытаются аппаратно воссоздать с той или иной степени точности механизмы, лежащие в основе мозга, которые на первый взгляд довольно просты: по густо провязанной и меняющейся со временем сети нейронов асинхронно и параллельно распространяются сигналы как ответ на внешние события.

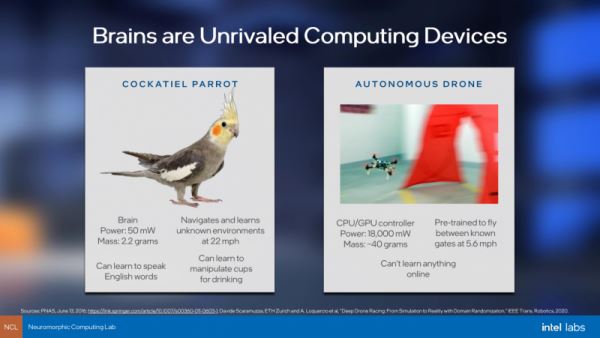

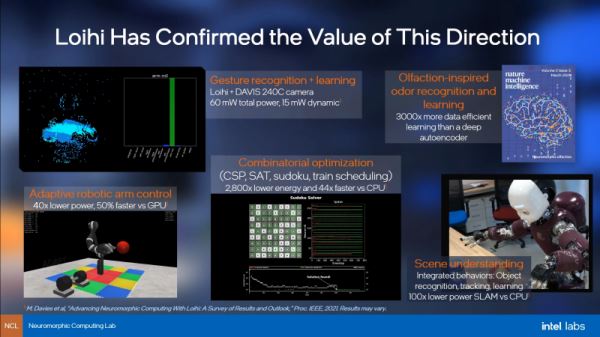

Попытки повторить это в рамках обычного «железа» можно считать достаточно успешными, ведь нейронными сетями сейчас никого не удивишь. Однако такие сети требуют затратного предварительного обучения на заранее размеченных данных, тогда как мозг учится «на лету». А с ростом сложности моделей остро встаёт вопрос энергоэффективности, причём не только обучения, но и исполнения.

«Вершиной эволюции» классических ИИ-ускорителей на сегодняшний день можно считать Cerebras WSE-2: чип размером с кремниевую пластину содержит 850 тыс. ядер и потребляет 15 кВт. Но и этого мало — по словам самих разработчиков, только кластер из таких чипов способен работать с ИИ-моделями, сравнимыми по масштабу с человеческим мозгом. И все эти ограничения призваны устранить именно нейроморфные системы.

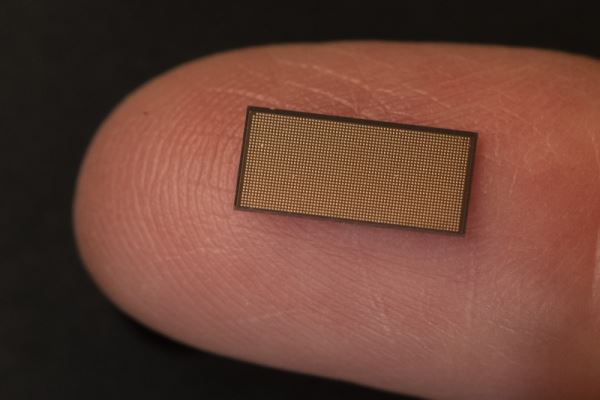

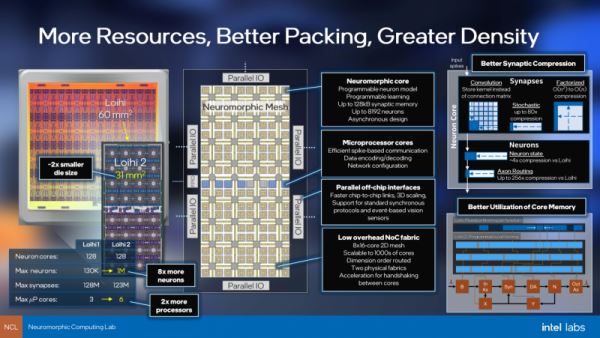

Loihi II изготавливается по EUV-техпроцессу Intel 4, который всё ещё находится в стадии разработки. Чип имеет площадь 31 мм2 и содержит 2,3 млрд транзисторов, а площадь одного ядра составляет 0,21 мм2, то есть плотность по сравнению с первым поколением выросла практически вдвое. Чип всё так же содержит 128 нейронных ядер, но число доступных нейронов выросло со 128 тыс. до 1 млн. Объём памяти на ядро слегка уменьшился, с 208 до 192 Кбайт, однако теперь банки памяти можно более гибко распределять между нейронами и синапсами, а компрессия позволяет ещё более эффективно использовать имеющийся объём.

Сами ядра тоже изменились. В первом поколении они были оптимизированы под конкретные импульсные нейронные сети, а теперь для каждого ядра есть собственный программируемый конвейер, а сами модели на уровне чипа задаются микрокодом. Кроме того, для состояния нейрона можно использовать до 4096 байт в зависимости от задач (ранее было только 24 байт). Число синапсов на чип уменьшилось со 128 до 12 млн, но они получили существенный апгрейд — для кодирования сигнала используется INT32-значение, а не бинарное (есть/нет).

Всё вместе это позволяет задействовать обучение (в том числе на лету) с третьим фактором. Тем не менее, набор инструкций нейроморфных ядер остался по-прежнему простым. Он включает базовые арифметические операции, сдвиги, ветвление, работу с памятью/регистрами и импульсами. Сами ядра объединены быстрой mesh-сетью 8×16, а за конфигурацию сети, (де-)кодирование данных и управлением передачей импульсов отвечают ещё шесть выделенных ядер (ранее их было только три) с аппаратным ускорением соответствующих задач.

Суммарный эффект от всех нововведений таков, что Loihi II быстрее Loihi первого поколения примерно на порядок. Более того, он получил улучшенные возможности масштабирования: до 1000 ядер на самом чипе, а также можно сформировать трёхмерную mesh-сеть из чипов благодаря шести выделенным I/O-контроллерам на каждом из них и вчетверо более быстрым линиям. А для связи с внешним миром теперь доступны стандартные интерфейсы SPI/AER, GPIO и ½.5/10GbE.

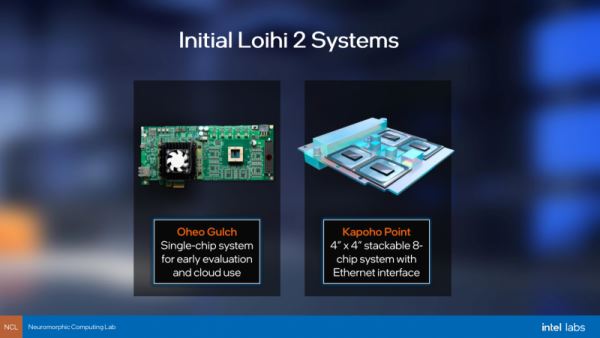

Первым устройством на базе Loihi II стала одночиповая карта Oheo Gulch, предназначенная для разработки и отладки ПО. Она пока что доступна только избранным партнёрам Intel в облаке Neuromorphic Research Cloud. Следующим устройством станет компактная (4” × 4”) плата Kapoho Point, которая несёт на борту уже восемь чипов Loihi II и предоставляет Ethernet и GPIO, а также различные интерфейсы для сенсоров и актуаторов. Платы можно будет напрямую объединять между собой для простого наращивания вычислительной мощности. В дальнейшем возможна интеграция чипов в гибридные SoC для различных задач, а также появление решений для ЦОД.

В целом, области применения и задачи новинок совпадают с теми, что сейчас обслуживают «классические» нейронные сети (с поправкой на энергоэффективность). Однако одного «железа» для распространения мало, поэтому Intel подготовила универсальный open source фреймворк LAVA, который позволит унифицировать разработку и подготовку моделей для практических любых аппаратных решений (не только нейроморфных) с учётом специфики конкретных архитектур.

Источник: 3dnews.ru