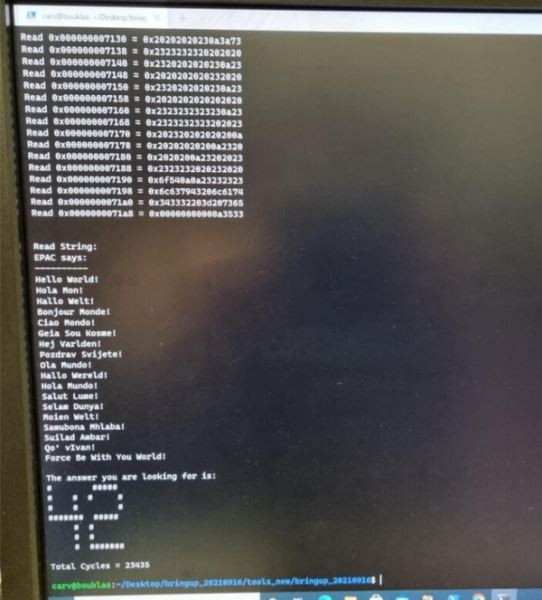

Консорциум European Processor Initiative (EPI), созданный с целью разработки отечественных чипов для будущих европейских суперкомпьютеров и обретения таким образом независимости от США в области высокопроизводительных вычислений (HPC), сообщил о получении первой партии тестовых процессоров EPAC 1.0 на архитектуре RISC-V и проведении их первых успешных испытаний. Со ссылкой на пресс-релиз EPI об этом сообщает портал TechPowerUp.

Источник изображений: TechPowerUp

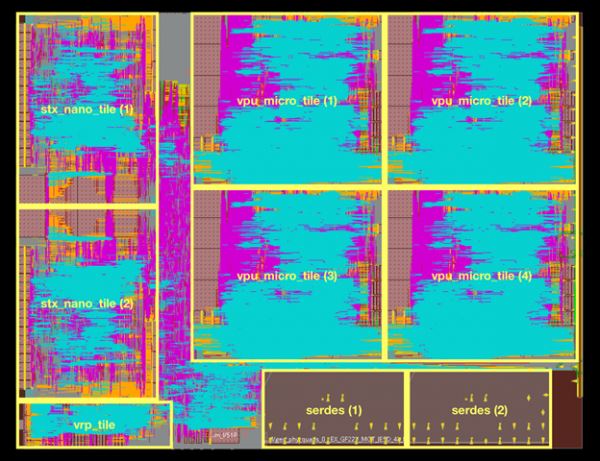

В составе чипов используются вычислительные ядра Avispado общего назначения с архитектурой RISC-V. Их разработала компания SemiDynamics. Четыре ядра объединены группы и дополнены блоком векторных вычислений (VPU), созданным Барселонским Суперкомпьютерным Центром (Испания) и Университетом Загреба (Хорватия).

В составе каждой группы также содержатся блоки Home Node (интерконнект) с кешем L2, обеспечивающие когерентную работу подсистем памяти, разработанные Техническим университетом Чалмерса (Швеция). Чип также содержит тензорно-стенсильный ускоритель STX, разработчиком которого является Институт Фраунгофера (Fraunhofer IIS). За разработку блока вычислений с изменяемой точностью (VRP) отвечала французская лаборатория CEA-LIST. Все ядра в составе нового процессора связаны высокоскоростным соединением, использующим SerDes-блоки от EXTOLL.

Первые 143 процессора EPAC были произведены на мощностях GlobalFoundries с использованием 22-нм техпроцесса FDX22, имеют площадь всего 27 мм2, используют упаковку FCBGA 22×22 и обладают тактовой частотой в 1 ГГц.

К настоящему моменту консорциум EPI объединяет 28 технических партнёров из 10 европейских стран.

Источник: 3dnews.ru